VVML - Specifying Workflows for Verification & Validation Methods

You can find here the slides for a lecture that I gave in the VALU3S' Summer School on Verification and Validation of Dependable Cyber-Physical Systems, held in Genova, Italy on 18th-20th July 2023 - https://valu3s.eu/summer-school-2023/.

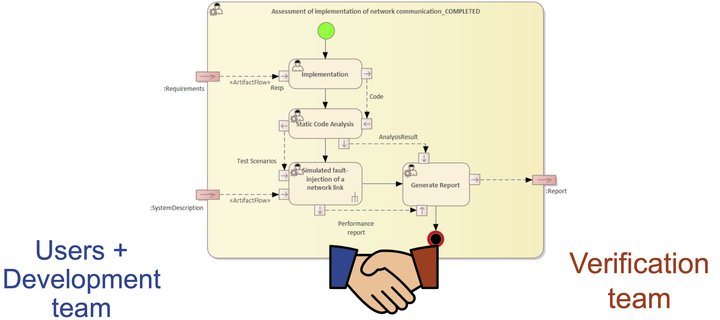

VVML (Verification & Validation Modelling Language) is a modelling language based on UML’s activity diagrams optimised to describe processes where formal methods are applied in concrete systems. This lecture describes an approach to formalise and to reason formally over correctness of workflows described using in VVML. The (informal) guidelines on how to build VVML workflows can be found online:

An interactive tool has been developed to animate the semantics proposed in the slides, and can be found online.

- Source code: https://www.github.com/cister-labs/coreVVML

- Use the tool: https://cister-labs.github.io/coreVVML